- Verilog Assignments

09 Sep 2021

In Verilog, there are various ways for assignment, due to the concurrent nature of the Verilog code. Also, to represent the combinational and sequential digital circuits, Verilog provides different ways for assignment which helps to model the hardware accurately.

As we know, Verilog has net and reg data types, which represent a wire and flip flop respectively. From hardware point of view, wires are driven continuously once the circuit is switched on, thus for every point of time wire will take the value which is fed into as it cannot retain any previous value. To represent this behaviour, Verilog provides continuous assignment. This will assign certain value to the wire at every time step.

Similarly, flip flops, are not driven continuously, rather it is driven at some clock edge or any other event, as flip flops retain the value until it is changed. This is the expected behaviour in sequential circuits. To represent this behaviour, Verilog provides procedural assignment, in which the assignment will be done only if certain event is triggered. Let’s see these assignments in detail.

Continuous Assignment

As discussed earlier this assignment is generally used for net data types. assign keyword is used for continuous assignment and is used directly inside the module, i.e., procedural blocks are not required for this type of assignment.

Procedural Assignment

Procedural assignments are used with flip flops, i.e., for sequential circuits. Thus, it can be used to drive only variables and not any net data type. Also, this type of assignment can only be used inside a procedural block, i.e., initial or always .

Procedural assignment can further be divided into 2 types:

Blocking Assignment

- Non-blocking Assignments

This type of assignment is the same as we see in all the programming language. As the name suggests, program flow will be blocked until the assignment is complete. This assignment is done using the help of = operator, which is also known as blocking assignment operator. Blocking assignment is executed in the Active region of the event semantics . As we know, the active region does not guarantee the order of execution, thus this type of assignment is prone to race conditions as discussed in previous article.

Non-blocking Assignment

This type of assignment, as name suggests, does not block the flow of program. The RHS of the assignment operation is calculated but it is not assigned to LHS. All the non-blocking assignments are executed at the end of the time-step in NBA region of event semantics and the LHS gets assigned with the calculated RHS. NBAs are done using <= operator which is also known as non-blocking assignment operator. As this assignment is done in NBA region, it helps prevent race around condition. We will see how this prevents race around condition with example later in this article.

Procedural Continuous Assignment

This is a continuous assignment which is used inside the procedural blocks. This is mainly used when we want to override the value of a variable or net. These types of assignments can be achieved using

- assign - deassign keyword

- force - release keyword.

Assign deassign keywords

These are used to override the value of a variable until the variable is de-assigned using deassign keyword. After de-assignment, the value of the variable will remain the same until it is re-assigned using procedural or procedural continuous assignment. These can be used only used when LHS is a variable or concatenation of variable.

In below example, the value of a is continuously incremented in the first initial block. In the second initial block, at t=17 , the value of a is overridden using assign keyword, and thus the value of a is not getting incremented. Once deassign is used at t=27 , the value of a starts getting incremented.

The value of a is not getting printed once the value of a is overridden, as $monitor prints only when the value of the variable changes. As assign does not let the value change, thus value of a is not getting printed even after a is incremented.

Force release keyword

These are same as that of assign-deassign statement but it can be used for both nets and variables. The LHS can be a bit-select, part-select of net but cannot be an array or a bit or part select of variables. These will override all other assignments until released.

In below example, b is continuously assigned ~a , i.e., inverse of a. In first initial block value of a is incremented and the value of b also changes. In second initial block, at t=15 value of a is overridden using force keyword. Value of b changes with response to a . At t=25 value of b[2:1] is overridden with force keyword, and thus now only the first and last bit of b can change. At t=35 variable a is released, and value of a can be changed, but net b is still not released, so only the first and the last bit of b changes with change in a . At t=45 net b is also released and now all bits of b is changed with change in a .

Prevention of race around condition

Race around condition, which was discussed in earlier article , can be prevented by using a non-blocking assignment. As we know in non-blocking assignment, the LHS is assigned in the non-blocking region of event semantics, which comes after the active regions, thus the value is determinate as all the calculations have been already done. Let’s understand this with an example.

In the 1st code, at the positive edge of clk , variable a is assigned a value whereas at the same time b is reading of value of a . As order of execution in active region is not guaranteed in Verilog, thus it can lead to a race around condition.

Whereas in 2nd code, as non-blocking assignment is used, thus 1 will not be assigned immediately to a . Now when, b access the variable a it will always read the previous value stored, in this case 0 . Thus, b will be assigned with 0 and a will be assigned with 1 at the send of the time step. Also note that for b to attain the value of a , it takes 2 cycles, thus at t=30, b = 1

1st code - having race around condition

2nd code - solution for race condition.

- Introduction to Verilog

- Verilog Event Semantics

- Basics of Verilog

- Verilog Syntax

- Data Types in Verilog

- Verilog Vectors

- Verilog Arrays

- Verilog Modules

- Verilog Ports

- Verilog Operators

- Verilog Procedural Blocks

- Different types of loops in Verilog

- Conditional Statements in Verilog

- Verilog functions and tasks

- Compiler Directives in Verilog

- Verilog System Functions

- Delays in Verilog

Using Continuous Assignment to Model Combinational Logic in Verilog

In this post, we talk about continuous assignment in verilog using the assign keyword. We then look at how we can model basic logic gates and multiplexors in verilog using continuous assignment.

There are two main classes of digital circuit which we can model in verilog – combinational and sequential .

Combinational logic is the simplest of the two, consisting solely of basic logic gates, such as ANDs, ORs and NOTs. When the circuit input changes, the output changes almost immediately (there is a small delay as signals propagate through the circuit).

In contrast, sequential circuits use a clock and require storage elements such as flip flops . As a result, output changes are synchronized to the circuit clock and are not immediate.

In this post, we talk about the techniques we can use to design combinational logic circuits in verilog. In the next post, we will discuss the techniques we use to model basic sequential circuits .

Continuous Assignment in Verilog

We use continuous assignment to drive data onto verilog net types in our designs. As a result of this, we often use continuous assignment to model combinational logic circuits.

We can actually use two different methods to implement continuous assignment in verilog.

The first of these is known as explicit continuous assignment. This is the most commonly used method for continuous assignment in verilog.

In addition, we can also use implicit continuous assignment, or net declaration assignment as it is also known. This method is less common but it can allow us to write less code.

Let's look at both of these techniques in more detail.

- Explicit Continuous Assignment

We normally use the assign keyword when we want to use continuous assignment in verilog. This approach is known as explicit continuous assignment.

The verilog code below shows the general syntax for continuous assignment using the assign keyword.

The <variable> field in the code above is the name of the signal which we are assigning data to. We can only use continuous assignment to assign data to net type variables.

The <value> field can be a fixed value or we can create an expression using the verilog operators we discussed in a previous post. We can use either variable or net types in this expression.

When we use continuous assignment, the <variable> value changes whenever one of the signals in the <value> field changes state.

The code snippet below shows the most basic example of continuous assignment in verilog. In this case, whenever the b signal changes states, the value of a is updated so that it is equal to b.

- Net Declaration Assignment

We can also use implicit continuous assignment in our verilog designs. This approach is also commonly known as net declaration assignment in verilog.

When we use net declaration assignment, we place a continuous assignment in the statement which declares our signal. This can allow us to reduce the amount of code we have to write.

To use net declaration assignment in verilog, we use the = symbol to assign a value to a signal when we declare it.

The code snippet below shows the general syntax we use for net declaration assignment.

The variable and value fields have the same function for both explicit continuous assignment and net declaration assignment.

As an example, the verilog code below shows how we would use net declaration assignment to assign the value of b to signal a.

Modelling Combinational Logic Circuits in Verilog

We use continuous assignment and the verilog operators to model basic combinational logic circuits in verilog.

To show we would do this, let's look at the very basic example of a three input and gate as shown below.

To model this circuit in verilog, we use the assign keyword to drive the data on to the and_out output. This means that the and_out signal must be declared as a net type variable, such as a wire.

We can then use the bit wise and operator (&) to model the behavior of the and gate.

The code snippet below shows how we would model this three input and gate in verilog.

This example shows how simple it is to design basic combinational logic circuits in verilog. If we need to change the functionality of the logic gate, we can simply use a different verilog bit wise operator .

If we need to build a more complex combinational logic circuit, it is also possible for us to use a mixture of different bit wise operators.

To demonstrate this, let's consider the basic circuit shown below as an example.

To model this circuit in verilog, we need to use a mixture of the bit wise and (&) and or (|) operators. The code snippet below shows how we would implement this circuit in verilog.

Again, this code is relatively straight forward to understand as it makes use of the verilog bit wise operators which we discussed in the last post.

However, we need to make sure that we use brackets to model more complex logic circuit. Not only does this ensure that the circuit operates properly, it also makes our code easier to read and maintain.

Modelling Multiplexors in Verilog

Multiplexors are another component which are commonly used in combinational logic circuits.

In verilog, there are a number of ways we can model these components.

One of these methods uses a construct known as an always block . We normally use this construct to model sequential logic circuits, which is the topic of the next post in this series. Therefore, we will look at this approach in more detail the next blog post.

In the rest of this post, we will look at the other methods we can use to model multiplexors.

- Verilog Conditional Operator

As we talked about in a previous blog, there is a conditional operator in verilog . This functions in the same way as the conditional operator in the C programming language.

To use the conditional operator, we write a logical expression before the ? operator which is then evaluated to see if it is true or false.

The output is assigned to one of two values depending on whether the expression is true or false.

The verilog code below shows the general syntax which the conditional operator uses.

From this example, it is clear how we can create a basic two to one multiplexor using this operator.

However, let's look at the example of a simple 2 to 1 multiplexor as shown in the circuit diagram below.

The code snippet below shows how we would use the conditional operator to model this multiplexor in verilog.

- Nested Conditional Operators

Although this is not common, we can also write code to build larger multiplexors by nesting conditional operators.

To show how this is done, let's consider a basic 4 to 1 multiplexor as shown in the circuit below.

To model this in verilog using the conditional operator, we treat the multiplexor circuit as if it were a pair of two input multiplexors.

This means one multiplexor will select between inputs A and B whilst the other selects between C and D. Both of these multiplexors use the LSB of the address signal as the address pin.

To create the full four input multiplexor, we would then need another multiplexor.

This takes the outputs from the first two multiplexors and uses the MSB of the address signal to select between them.

The code snippet below shows the simplest way to do this. This code uses the signals mux1 and mux2 which we defined in the last example.

However, we could easily remove the mux1 and mux2 signals from this code and instead use nested conditional operators.

This reduces the amount of code that we would have to write without affecting the functionality.

The code snippet below shows how we would do this.

As we can see from this example, when we use conditional operators to model multiplexors in verilog, the code can quickly become difficult to understand. Therefore, we should only use this method to model small multiplexors.

- Arrays as Multiplexors

It is also possible for us to use verilog arrays to build simple multiplexors.

To do this we combine all of the multiplexor inputs into a single array type and use the address to point at an element in the array.

To get a better idea of how this works in practise, let's consider a basic four to one multiplexor as an example.

The first thing we must do is combine our input signals into an array. There are two ways in which we can do this.

Firstly, we can declare an array and then assign all of the individual bits, as shown in the verilog code below.

Alternatively we can use the verilog concatenation operator , which allows us to assign the entire array in one line of code.

To do this, we use a pair of curly braces - { } - and list the elements we wish to include in the array inside of them.

When we use the concatenation operator we can also declare and assign the variable in one statement, as long as we use a net type.

The verilog code below shows how we can use the concatenation operator to populate an array.

As verilog is a loosely typed language , we can use the two bit addr signal as if it were an integer type. This signal then acts as a pointer that determines which of the four elements to select.

The code snippet below demonstrates this method in practise. As the mux output is a wire, we must use continuous assignment in this instance.

What is the difference between implicit and explicit continuous assignment?

When we use implicit continuous assignment we assign the variable a value when we declare. When we use explicit continuous assignment we use the assign keyword to assign a value.

Write the code for a 2 to 1 multiplexor using any of the methods discussed we discussed.

Write the code for circuit below using both implicit and explicit continuous assignment.

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Table of Contents

Sign up free for exclusive content.

Don't Miss Out

We are about to launch exclusive video content. Sign up to hear about it first.

- Interview Q

Verilog Tutorial

The RHS can contain any expression that evaluates to a final value while the LHS indicates a variable or net to which RHS's value is being assigned.

Procedural Assignment

Procedural assignments occur within procedures such as initial, always, task , and functions are used to place values onto variables. The variable will hold the value until the next assignment to the same variable.

The value will be placed onto the variable when the simulation executes this statement during simulation time. This can be modified and controlled the way we want by using control flow statements such as if-else-if, looping , and case statement mechanisms.

Variable Declaration Assignment

An initial value can be placed onto a variable at the time of its declaration. The assignment does not have the duration and holds the value until the next assignment to the same variable happens.

NOTE: The variable declaration assignments to an array are not allowed.

If the variable is initialized during declaration and at 0 times in an initial block as shown below, the order of evaluation is not guaranteed, and hence can have either 8'h05 or 8'hee.

Continuous Assignment

This is used to assign values onto scalar and vector nets. And it happens whenever there is a change in the RHS.

It provides a way to model combinational logic without specifying an interconnection of gates and makes it easier to drive the net with logical expressions.

Whenever b or c changes its value, the whole expression in RHS will be evaluated and updated with the new value.

Net Declaration Assignment

This allows us to place a continuous assignment on the same statement that declares the net.

NOTE: Only one declaration assignment is possible because a net can be declared only once.

Procedural continuous assignment.

These are procedural statements that allow expressions to be continuously assigned to variables or nets. And these are the two types.

1. Assign deassign: It will override all procedural assignments to a variable and deactivate it using the same signal with deassign .

The value of the variable will remain the same until the variable gets a new value through a procedural or procedural continuous assignment.

The LHS of an assign statement cannot be a part-select, bit-select, or an array reference, but it can be a variable or a combination of the variables.

2. Force release: These are similar to the assign deassign statements but can also be applied to nets and variables.

The LHS can be a bit-select of a net, part-select of a net, variable, or a net but cannot be the reference to an array and bit or part select of a variable.

The force statement will override all other assignments made to the variable until it is released using the release keyword.

- Send your Feedback to [email protected]

Help Others, Please Share

Learn Latest Tutorials

Transact-SQL

Reinforcement Learning

R Programming

React Native

Python Design Patterns

Python Pillow

Python Turtle

Preparation

Verbal Ability

Interview Questions

Company Questions

Trending Technologies

Artificial Intelligence

Cloud Computing

Data Science

Machine Learning

B.Tech / MCA

Data Structures

Operating System

Computer Network

Compiler Design

Computer Organization

Discrete Mathematics

Ethical Hacking

Computer Graphics

Software Engineering

Web Technology

Cyber Security

C Programming

Control System

Data Mining

Data Warehouse

Procedural continuous assignments

Till now we have seen two types of assignments i.e. continuous assignment and procedural assignment .

The continuous assignment is used to drive net data type variables using the ‘assign’ statements whereas procedural assignments are used to drive reg data type variables using initial and always block statements.

Verilog also provides a third type of assignment i.e. procedural continuous assignment that drives net or reg data type variables for a certain period of time by overriding the existing assignments.

There are two types of procedural continuous assignments

assign and deassign

Force and release.

The assign and deassign statements control reg type variable values by overriding existing procedural assignments for a limited time period. After the execution of the deassign statement, another procedural or procedural continuous assignment can change the variable value once again, till then the previous value can hold.

The d1 = 3 is assigned at #5 time units and deassign at #10 time units.The d1 = 3 retains till next assignment d1 = 7 happens at 20 time units.

The force and release statements control net and reg data type variable values by overriding existing procedural, continuous or procedural continuous assignments for a limited time period. After the execution of the release statement for the reg data type variable, another procedural or procedural continuous assignment can change the variable value once again, till then the previous value can hold. The value of the previous continuous assignment retains in the case of the net data type variable.

The d1 belongs to the reg data type and d2 belongs to the net data type. Both variables are forced at #5 time units and released at #10 time units Once, it is released,

- The d1 value remains the same (d1 = 3) until it is changed to d1 = 7 at 20 time units.

- The d2 value holds a previously assigned value using continuous assignment (d2 = 2).

Verilog Tutorials

Verilog (Part 1)

- First Online: 20 October 2023

Cite this chapter

- Brock J. LaMeres 2

335 Accesses

Based on the material presented in Chap. 4, there are a few observations about logic design that is apparent. First, the size of logic circuitry can scale quickly to the point where it is difficult to design by hand. Second, the process of moving from a high-level description of how a circuit works (e.g., a truth table) to a form that is ready to be implemented with real circuitry (e.g., a minimized logic diagram) is straightforward and well-defined. Both of these observations motivate the use of computer-aided design (CAD) tools to accomplish logic design. This chapter introduces hardware description languages (HDLs) as a means to describe digital circuitry using a text-based language. HDLs provide a means to describe large digital systems without the need for schematics, which can become impractical in very large designs. HDLs have evolved to support logic simulation at different levels of abstraction. This provides designers the ability to begin designing and verifying the functionality of large systems at a high level of abstraction and postpone the details of the circuit implementation until later in the design cycle. This enables a top-down design approach that is scalable across different logic families. HDLs have also evolved to support automated synthesis , which allows the CAD tools to take a functional description of a system (e.g., a truth table) and automatically create the gate-level circuitry to be implemented in real hardware. This allows designers to focus their attention on designing the behavior of a system and not spend as much time performing the formal logic synthesis steps that were presented in Chap. 4. The intent of this chapter is to introduce HDLs and their use in the modern digital design flow. This chapter covers the basics of designing combinational logic in an HDL and also hierarchical design. The more advanced concepts of HDLs such as sequential logic design, high-level abstraction, and test benches are covered later so that the reader can get started quickly using HDLs to gain experience with the languages and design flow.

There are two dominant hardware description languages in use today. They are VHDL and Verilog. VHDL stands for v ery high-speed integrated circuit h ardware d escription l anguage . Verilog is not an acronym but rather a trade name. The use of these two HDLs is split nearly equally within the digital design industry. Once one language is learned it is simple to learn the other language, so the choice of the HDL to learn first is somewhat arbitrary. In this text, we will use Verilog to learn the concepts of a HDL. Verilog is more similar to the programming language C and less strict in its type casting than VHDL. Verilog is also widely used in custom integrated circuit design so there is a great deal of documentation and examples readily available online. The goal of this chapter is to provide an understanding of the basic principles of hardware description languages.

This is a preview of subscription content, log in via an institution to check access.

Access this chapter

- Available as PDF

- Read on any device

- Instant download

- Own it forever

- Available as EPUB and PDF

- Durable hardcover edition

- Dispatched in 3 to 5 business days

- Free shipping worldwide - see info

Tax calculation will be finalised at checkout

Purchases are for personal use only

Institutional subscriptions

Author information

Authors and affiliations.

Department of Electrical & Computer Engineering, Montana State University, Bozeman, MT, USA

Brock J. LaMeres

You can also search for this author in PubMed Google Scholar

Rights and permissions

Reprints and permissions

Copyright information

© 2024 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this chapter

LaMeres, B.J. (2024). Verilog (Part 1). In: Introduction to Logic Circuits & Logic Design with Verilog. Springer, Cham. https://doi.org/10.1007/978-3-031-43946-9_5

Download citation

DOI : https://doi.org/10.1007/978-3-031-43946-9_5

Published : 20 October 2023

Publisher Name : Springer, Cham

Print ISBN : 978-3-031-43945-2

Online ISBN : 978-3-031-43946-9

eBook Packages : Engineering Engineering (R0)

Share this chapter

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

- Publish with us

Policies and ethics

- Find a journal

- Track your research

- The Verilog-AMS Language

- Continuous Assigns

Continuous Assigns

A module may have any number of continuous assign statements. Continuous assign statements are used to drive values on to wires. For example:

This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire. The continuous assign statement is not a procedural statement and so must be used at the module level; it cannot be placed in an initial or always process.

You can add delay to a continuous assign statement as follows:

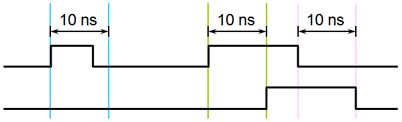

In this case, the value of a changes 10 units of time after the expression b & c changes. Continuous assign statement implement inertial delay, meaning that continuous assign statements swallow glitches. This is illustrated below with the assumption that the unit of time is 1ns.

It is possible to specify up to three delay values on a continuous assignment:

When you specify more than one:

The first delay refers to the transition to the 1 value (rise delay).

The second delay refers to the transition to the 0 value (fall delay).

The third delay refers to the transition to the high-impedance value.

When a value changes to the unknown (x) value, the delay is the smallest of the delays specified.

If only two delays are specified, then the delay to high-impedance is the smallest of the two values specified.

Verilog Operators

Data that cannot be processed is quite useless, there'll always be some form of calculation required in digital circuits and computer systems. Let's look at some of the operators in Verilog that would enable synthesis tools realize appropriate hardware elements.

Verilog Arithmetic Operators

If the second operand of a division or modulus operator is zero, then the result will be X. If either operand of the power operator is real, then the result will also be real. The result will be 1 if the second operand of a power operator is 0 (a 0 ).

An example of how arithmetic operators are used is given below.

Verilog Relational Operators

An expression with the relational operator will result in a 1 if the expression is evaluated to be true, and 0 if it is false. If either of the operands is X or Z, then the result will be X. Relational operators have a lower precedence than arithmetic operators and all relational operators have the same precedence.

Verilog Equality Operators

Equality operators have the same precedence amongst them and are lower in precedence than relational operators. The result is 1 if true, and 0 if false. If either of the operands of logical-equality (==) or logical-inequality (!=) is X or Z, then the result will be X. You may use case-equality operator (===) or case-inequality operator (!==) to match including X and Z and will always have a known value.

Verilog Logical Operators

The result of a logical and (&&) is 1 or true when both its operands are true or non-zero. The result of a logical or (||) is 1 or true when either of its operands are true or non-zero. If either of the operands is X, then the result will be X as well. The logical negation (!) operator will convert a non-zero or true operand into 0 and a zero or false operand into 1, while an X will remain as an X.

Verilog Bitwise Operators

This operator will combine a bit in one operand with its corresponding bit in the other operand to calculate a single bit result.

Verilog Shift Operators

- Logical shift operators : and >>

- Arithmetic shift operators : and >>>

IMAGES

VIDEO

COMMENTS

This is used to assign values onto scalar and vector nets and happens whenever there is a change in the RHS. It provides a way to model combinational logic without specifying an interconnection of gates and makes it easier to drive the net with logical expressions. // Example model of an AND gate. wire a, b, c;

Evaluate b&(~c) but defer assignment of z 1. Evaluate a | b, assign result tox x 2. Evaluate a^b^c, assign result to y 3. Evaluate b&(~c), assign result to zz I. Blocking vs. Nonblocking Assignments • Verilog supports two types of assignments within always blocks, with subtly different behaviors. • Blocking assignment: evaluation and ...

Procedural assignments are used for updating register data types and memory data types. The expression in a blocking procedural assignment is evaluated and assigned when the statement is encountered.

Blocking Assignment. A blocking assignment evaluates the expression on its right hand side and then immediately assigns the value to the variable on its left hand side: a = b + c; It is also possible to add delay to a blocking assignment. For example: a = #10 b + c; In this case, the expression on the right hand side is evaluated and the value ...

use Verilog's operators and continuous assignment statements: Conceptually assign's are evaluated continuously, so whenever a value used in the RHS changes, the RHS is re-evaluated and the value of the wire/bus specified on the LHS is updated. This type of execution model is called "dataflow" since evaluations

Continuous Assignment. Continuous assignment is used to drive a value on to a net in dataflow modeling. The net can be a vector or scalar, indexed part select, constant bit or part select of a vector. Concatenation is also supported with scalar vector types. module Conti_Assignment (addr1,addr2,wr,din,valid1,valid2,dout); input [31:0] addr1,addr2;

1) <= non-blocking and is performed on every positive edge of clock. these are evaluated in parallel so no guarantee of order. An example of this would be a register. 2) assign = continual assignment to wire outside an always statement. value of LHS is updated when RHS changes. 3) = blocking assignment, inside always statements enforces ...

Verilog Assignments. In Verilog, there are various ways for assignment, due to the concurrent nature of the Verilog code. Also, to represent the combinational and sequential digital circuits, Verilog provides different ways for assignment which helps to model the hardware accurately. As we know, Verilog has net and reg data types, which ...

Verilog is a hardware description language (HDL) that is used to describe digital systems and circuits in the form of code. It was developed by Gateway Design Automation in the mid-1980s and later acquired by Cadence Design Systems. Verilog is widely used for design and verification of digital and mixed-signal systems, including both ...

July 7, 2020. In this post, we talk about the most commonly used data types in Verilog. This includes a discussion of data respresentation, net types, variables types, vectors types and arrays. Although verilog is considered to be a loosely typed language, we must still declare a data type for every port or signal in our verilog design.

The verilog code below shows the general syntax for continuous assignment using the assign keyword. assign <variable> = <value>; The <variable> field in the code above is the name of the signal which we are assigning data to. We can only use continuous assignment to assign data to net type variables.

Assignment. A assignment evaluates the expression on its right hand side and then immediately assigns the value to the variable on its left hand side: a = b + c; The target (left side) of an analog assignment statement may only be a integer or real variable. It may not be signal or a wire.

And these are the two types. 1. Assign deassign: It will override all procedural assignments to a variable and deactivate it using the same signal with deassign. The value of the variable will remain the same until the variable gets a new value through a procedural or procedural continuous assignment.

12.2. Procedural Statements¶. There are two types of procedural statements, the always block and the initial block. In Verilog there may be several always blocks and they are executed in parallel. The initial block is used for simulation, it can't be synthesized and it executes only once in the start a simulation.. The always block executes when its pre-defined funtions, or its inputs changes.

The continuous assignment is used to drive net data type variables using the 'assign' statements whereas procedural assignments are used to drive reg data type variables using initial and always block statements. Verilog also provides a third type of assignment i.e. procedural continuous assignment that drives net or reg data type variables ...

When assigning between different types, Verilog will automatically truncate or add leading bits as necessary to make the assignment work. The following examples illustrate how Verilog handles a few assignments between different types. Assume that a variable called ABC_TB has been declared as type reg[2:0]. Example:

Continuous assign statements are used to drive values on to wires. For example: assign a = b & c; This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire.

In LRM, the type: specifier and default: specifier have to apply to sub-array elements or every field of a structure either the type matches for type: or default: values. However, for the union type, it represents either int or bit vector. So it could apply 2 to int type and also apply 1 to the bit vector type.

Verilog Relational Operators. An expression with the relational operator will result in a 1 if the expression is evaluated to be true, and 0 if it is false. If either of the operands is X or Z, then the result will be X. Relational operators have a lower precedence than arithmetic operators and all relational operators have the same precedence ...